量子回路の最適化

Toshinari Itoko (2024年6月21日)

元の講義の PDF をダウンロード できます。なお、コードスニペットは静的な画像であるため、一部が非推奨になっている場合があります。

この実験を実行するおおよその QPU 時間は 15 秒です。

(注: パート 2 の一部のセルは、Matthew Treinish(Qiskit メンテナー)が作成した「Qiskit Deep dive」ノートブックから転用しています)

# Added by doQumentation — required packages for this notebook

!pip install -q qiskit qiskit-aer qiskit-ibm-runtime

# !pip install 'qiskit[visualization]'

# !pip install qiskit_ibm_runtime qiskit_aer

# !pip install jupyter

# !pip install matplotlib pylatexenc pydot pillow

import qiskit

qiskit.__version__

'2.0.2'

import qiskit_ibm_runtime

qiskit_ibm_runtime.__version__

'0.40.1'

import qiskit_aer

qiskit_aer.__version__

'0.17.1'

1. はじめに

このレッスンでは、量子コンピューティングにおける回路最適化のさまざまな側面について解説します。具体的には、Qiskit に組み込まれた最適化設定を使って回路最適化の効果を確認します。次に、特定のアプリケーション分野の専門家として、回路をスマートに構築する方法を深掘りします。最後に、トランスパイル中に何が起きているかを詳しく見ながら、回路をどのように最適化するかを確認します。

2. 回路の最適化が重要な理由

まず、最適化あり・なしの場合で 5 量子ビット GHZ 状態 () の準備回路を実行した結果を比較します。

from qiskit.circuit import QuantumCircuit

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

from qiskit.primitives import BackendSamplerV2 as Sampler

from qiskit_ibm_runtime.fake_provider import FakeBrisbane

backend = FakeBrisbane()

まず、以下のように単純に合成した GHZ 回路を使います。

num_qubits = 5

ghz_circ = QuantumCircuit(num_qubits)

ghz_circ.h(0)

[ghz_circ.cx(0, i) for i in range(1, num_qubits)]

ghz_circ.measure_all()

ghz_circ.draw("mpl")

2.1 最適化レベル

optimization_level は 0〜3 の 4 段階が用意されています。最適化レベルが高いほど、回路の最適化に多くの計算コストが使われます。レベル 0 は最適化を行わず、選択したバックエンドで回路を実行するのに必要な最小限の処理のみを行います。レベル 3 は最も多くの処理(および通常は実行時間)をかけて回路を最適化しようとします。レベル 1 がデフォルトの最適化レベルです。

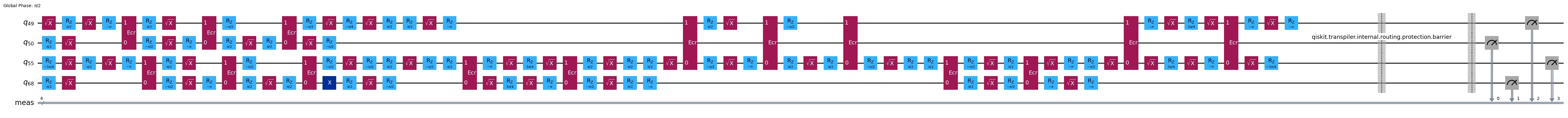

最適化なし (optimization_level=0) と最適化あり (optimization_level=2) で回路をトランスパイルします。トランスパイルされた回路の長さに大きな違いが見られます。

pm0 = generate_preset_pass_manager(

optimization_level=0, backend=backend, seed_transpiler=777

)

pm2 = generate_preset_pass_manager(

optimization_level=2, backend=backend, seed_transpiler=777

)

circ0 = pm0.run(ghz_circ)

circ2 = pm2.run(ghz_circ)

print("optimization_level=0:")

display(circ0.draw("mpl", idle_wires=False, fold=-1))

print("optimization_level=2:")

display(circ2.draw("mpl", idle_wires=False, fold=-1))

optimization_level=0:

optimization_level=2:

2.2 演習

optimization_level=1 も試して、上記の 2 つの結果と比較してみましょう。上のコードを修正して実行してください。

解答:

pm1 = generate_preset_pass_manager(

optimization_level=1, backend=backend, seed_transpiler=777

)

circ1 = pm1.run(ghz_circ)

print("optimization_level=1:")

display(circ1.draw("mpl", idle_wires=False, fold=-1))

optimization_level=1:

フェイクバックエンド(ノイズシミュレーション)で実行します。実機バックエンドでの実行方法については、付録 1 を参照してください。

# run the circuits on the fake backend (noisy simulator)

sampler = Sampler(backend=backend)

job = sampler.run([circ0, circ2], shots=10000)

print(f"Job ID: {job.job_id()}")

Job ID: 93a4ac70-e3ea-44ad-aea9-5045840c9076

# get results

result = job.result()

unoptimized_result = result[0].data.meas.get_counts()

optimized_result = result[1].data.meas.get_counts()

from qiskit.visualization import plot_histogram

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, unoptimized_result, optimized_result]],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"with optimization",

],

)

3. 回路の合成が重要な理由

次に、異なる方法で合成された 2 つの 5 量子ビット GHZ 状態 () 準備回路の実行結果を比較します。

# Original GHZ circuit (naive synthesis)

ghz_circ.draw("mpl")

# A cleverly-synthesized GHZ circuit

ghz_circ2 = QuantumCircuit(5)

ghz_circ2.h(2)

ghz_circ2.cx(2, 1)

ghz_circ2.cx(2, 3)

ghz_circ2.cx(1, 0)

ghz_circ2.cx(3, 4)

ghz_circ2.measure_all()

ghz_circ2.draw("mpl")

# transpile both with the same optimization level 2

circ_org = pm2.run(ghz_circ)

circ_new = pm2.run(ghz_circ2)

print("original synthesis:")

display(circ_org.draw("mpl", idle_wires=False, fold=-1))

print("new synthesis:")

display(circ_new.draw("mpl", idle_wires=False, fold=-1))

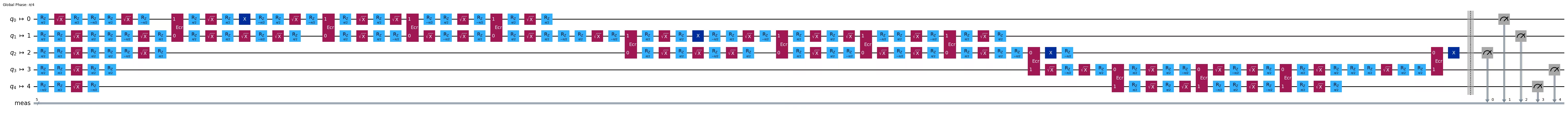

original synthesis:

new synthesis:

新しい合成ではより浅い回路が生成されます。なぜでしょうか?

これは、新しい回路が線形接続の量子ビット上に配置できるためです。つまり、IBM® Brisbane のヘビーヘキサゴン結合グラフ上でも配置可能です。一方、元の回路はスター型の接続(次数 4 のノード)を必要とするため、最大でも次数 3 のノードしか持たないヘビーヘックス結合グラフには配置できません。その結果、元の回路では量子ビットのルーティングが必要となり、SWAP ゲートが追加されてゲート数が増加します。

新しい回路で行ったことは、「結合制約を考慮した」回路合成の手動実装と見なすことができます。つまり、回路合成と回路マッピングを同時に手動で解いているのです。

# run the circuits

sampler = Sampler(backend=backend)

job = sampler.run([circ_org, circ_new], shots=10000)

print(f"Job ID: {job.job_id()}")

Job ID: 19d635b0-4d8b-44c2-a76e-49e4b9078b1b

# get results

result = job.result()

synthesis_org_result = result[0].data.meas.get_counts()

synthesis_new_result = result[1].data.meas.get_counts()

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[

result

for result in [

sim_result,

unoptimized_result,

synthesis_org_result,

synthesis_new_result,

]

],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"synthesis_org",

"synthesis_new",

],

)

一般に、回路の合成はアプリケーションに依存するため、すべてのアプリケーションをソフトウェアがカバーするのは非常に困難です。Qiskit トランスパイラーには GHZ 状態準備回路を合成する機能がたまたまありません。このような場合、上で示したような手動の回路合成を検討する価値があります。

このセクションでは、次のトイサンプル回路を使って Qiskit トランスパイラーの動作の詳細を見ていきます。

# Build a toy example circuit

from math import pi

import itertools

from qiskit.circuit import QuantumCircuit

from qiskit.circuit.library import excitation_preserving

circuit = QuantumCircuit(4, name="Example circuit")

circuit.append(excitation_preserving(4, reps=1, flatten=True), range(4))

circuit.measure_all()

value_cycle = itertools.cycle([0, pi / 4, pi / 2, 3 * pi / 4, pi, 2 * pi])

circuit.assign_parameters(

[x[1] for x in zip(range(len(circuit.parameters)), value_cycle)], inplace=True

)

circuit.draw("mpl")

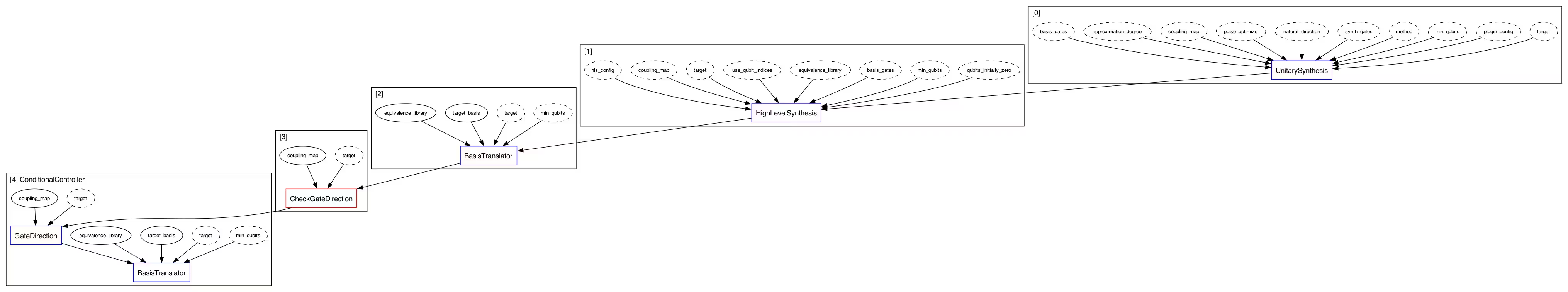

3.1 Qiskitトランスパイルフロー全体を描画する

optimization_level=1 のトランスパイラーパス(タスク)を確認します。

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

# There is no need to read this entire image, but this outputs all the steps in the transpile() call

# for optimization level 1

pm = generate_preset_pass_manager(1, backend, seed_transpiler=42)

pm.draw()

フローは6つのステージで構成されています。

print(pm.stages)

('init', 'layout', 'routing', 'translation', 'optimization', 'scheduling')

3.2 個別ステージを描画する

まず、init ステージで実行されるすべてのタスク(トランスパイラーパス)を描画してみましょう。

pm.init.draw()

各ステージを個別に実行することができます。Circuit に対して init ステージを実行してみましょう。ロガーを有効にすることで、実行の詳細を確認できます。

import logging

logger = logging.getLogger()

logger.setLevel("INFO")

init_out = pm.init.run(circuit)

init_out.draw("mpl", fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: UnitarySynthesis - 0.03576 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: HighLevelSynthesis - 0.16618 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 0.07176 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.27299 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.00811 (ms)

3.3 演習

上記のセルを修正して、layout ステージのパスを描画し、init ステージの出力 Circuit(init_out)に対してそのステージを実行してみてください。

解答:

display(pm.layout.draw())

layout_out = pm.layout.run(init_out)

layout_out.draw("mpl", idle_wires=False, fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: SetLayout - 0.01001 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: TrivialLayout - 0.07129 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: CheckMap - 0.08917 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: VF2Layout - 1.24431 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BarrierBeforeFinalMeasurements - 0.02599 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: SabreLayout - 5.11169 (ms)

translation ステージについても同様に行ってみてください。

解答:

display(pm.translation.draw())

basis_out = pm.translation.run(layout_out)

basis_out.draw("mpl", idle_wires=False, fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: UnitarySynthesis - 0.03386 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: HighLevelSynthesis - 0.02718 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 2.64192 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: CheckGateDirection - 0.02217 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GateDirection - 0.36502 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 0.64778 (ms)

注意:個々のステージは必ずしも独立して実行できるとは限りません(前のステージからの情報を引き継ぐ必要があるものもあります)。

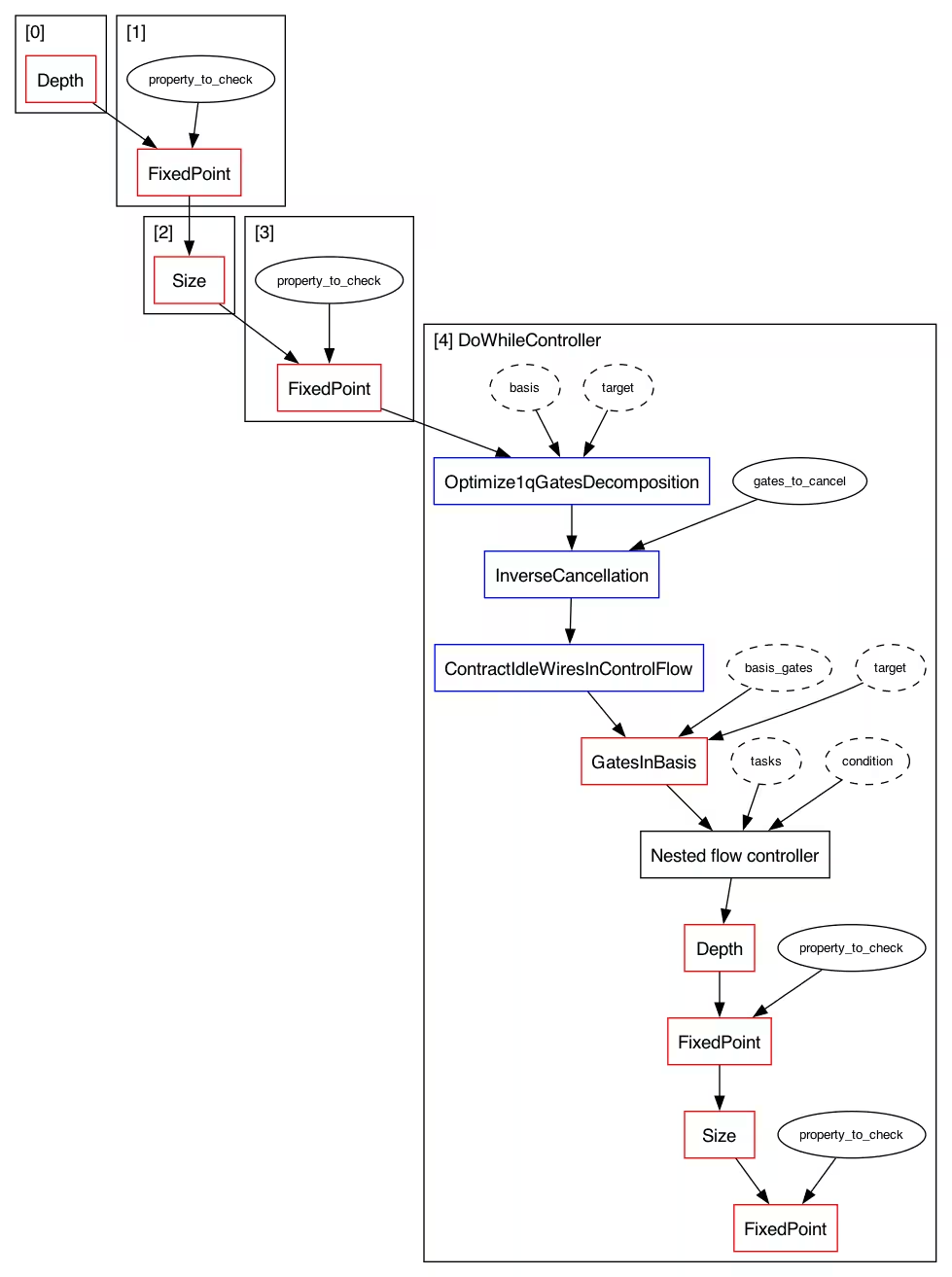

3.4 最適化ステージ

パイプラインの最後のデフォルトステージは最適化です。ターゲット向けに Circuit を埋め込んだ後、Circuit はかなり大きく拡張されています。これは主に、基底変換や SWAP 挿入における等価関係の非効率性によるものです。最適化ステージは Circuit のサイズと深さを最小化することを目的としており、出力が収束するまで一連のパスを do while ループで繰り返し実行します。

# pm.pre_optimization.draw()

pm.optimization.draw()

logger = logging.getLogger()

logger.setLevel("INFO")

opt_out = pm.optimization.run(basis_out)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.30112 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.03195 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.01216 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.01001 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Optimize1qGatesDecomposition - 0.63729 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.41723 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.01192 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GatesInBasis - 0.05484 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.08583 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.20599 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.00787 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00715 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Optimize1qGatesDecomposition - 0.16809 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.17190 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.00691 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GatesInBasis - 0.02408 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.04935 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00525 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.00620 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00286 (ms)

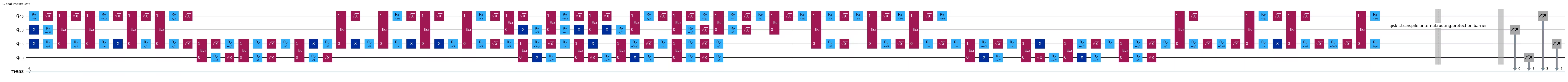

opt_out.draw("mpl", idle_wires=False, fold=-1)

4. 詳細な例

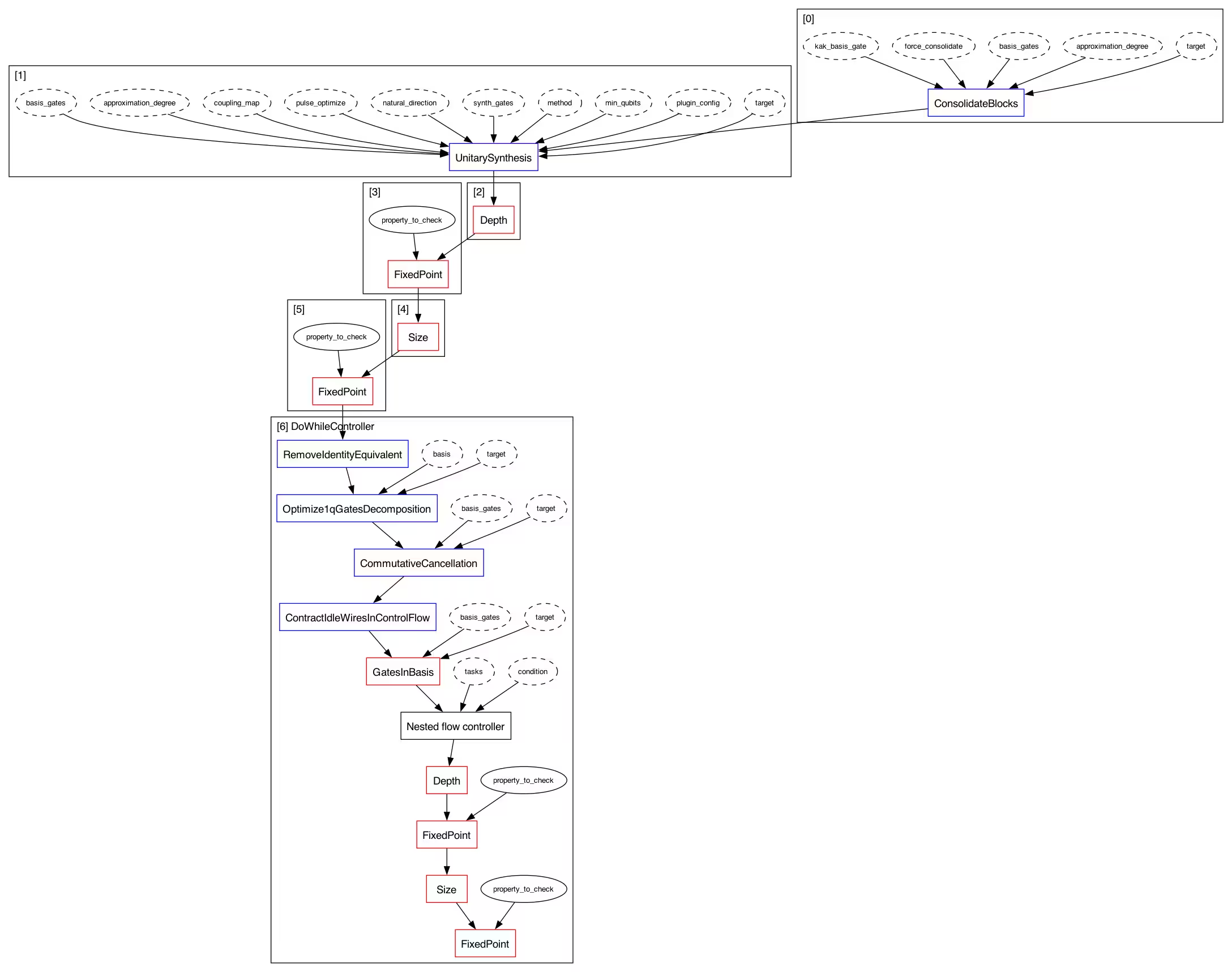

4.1 2量子ビットユニタリー合成による2量子ビットブロック最適化

レベル2および3では、さらなる最適化のために追加のパス(Collect2qBlocks、ConsolidateBlocks、UnitarySynthesis)が利用可能です。特に2量子ビットブロック最適化が行われます(レベル1の上記フローと比較して、レベル2の最適化ステージフローを確認してください)。

2量子ビットブロック最適化は2つのステップで構成されています。2量子ビットブロックの収集・統合と、2量子ビットユニタリー行列の合成です。

pm2 = generate_preset_pass_manager(2, backend, seed_transpiler=42)

pm2.optimization.draw()

from qiskit.transpiler import PassManager

from qiskit.transpiler.passes import (

Collect2qBlocks,

ConsolidateBlocks,

UnitarySynthesis,

)

# Collect 2q blocks and consolidate to unitary when we expect that we can reduce the 2q gate count for that unitary

consolidate_pm = PassManager(

[

Collect2qBlocks(),

ConsolidateBlocks(target=backend.target),

]

)

display(basis_out.draw("mpl", idle_wires=False, fold=-1))

consolidated = consolidate_pm.run(basis_out)

consolidated.draw("mpl", idle_wires=False, fold=-1)

# Synthesize unitaries

UnitarySynthesis(target=backend.target)(consolidated).draw(

"mpl", idle_wires=False, fold=-1

)

logger.setLevel("WARNING")

第2部では、実際の量子コンパイラーフローはシンプルではなく、多くのパス(タスク)で構成されていることを確認しました。これは主に、幅広いアプリケーション Circuit に対するパフォーマンスを確保し、ソフトウェアの保守性を維持するために必要なソフトウェアエンジニアリングによるものです。Qiskit Transpiler はほとんどの場合に有効に機能しますが、Qiskit Transpiler による最適化が不十分と感じた場合には、第1部で示したようなアプリケーション固有の Circuit 最適化を研究する良い機会かもしれません。Transpiler 技術は進化し続けており、皆さんの研究開発への貢献を歓迎します。

from qiskit.circuit import QuantumCircuit

from qiskit_ibm_runtime import QiskitRuntimeService, Sampler

service = QiskitRuntimeService()

backend = service.backend("ibm_brisbane")

sampler = Sampler(backend)

circ = QuantumCircuit(3)

circ.ccx(0, 1, 2)

circ.measure_all()

circ.draw("mpl")

sampler.run([circ]) # IBMInputValueError will be raised

4.2 Circuit 最適化の重要性

まず、最適化あり・なしで5 Qubit GHZ 状態()の準備 Circuit を実行した結果を比較します。

from qiskit.circuit import QuantumCircuit

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

from qiskit_ibm_runtime import QiskitRuntimeService, Sampler

service = QiskitRuntimeService()

# backend = service.backend('ibm_brisbane')

backend = service.least_busy(

operational=True, simulator=False, min_num_qubits=127

) # Eagle

backend

まず、次のように素直に合成された GHZ Circuit を使用します。

num_qubits = 5

ghz_circ = QuantumCircuit(num_qubits)

ghz_circ.h(0)

[ghz_circ.cx(0, i) for i in range(1, num_qubits)]

ghz_circ.measure_all()

ghz_circ.draw("mpl")

最適化なし(optimization_level=0)と最適化あり(optimization_level=2)で Circuit をトランスパイルします。

ご覧のように、トランスパイル後の Circuit の長さには大きな差があります。

pm0 = generate_preset_pass_manager(

optimization_level=0, backend=backend, seed_transpiler=777

)

pm2 = generate_preset_pass_manager(

optimization_level=2, backend=backend, seed_transpiler=777

)

circ0 = pm0.run(ghz_circ)

circ2 = pm2.run(ghz_circ)

print("optimization_level=0:")

display(circ0.draw("mpl", idle_wires=False, fold=-1))

print("optimization_level=2:")

display(circ2.draw("mpl", idle_wires=False, fold=-1))

optimization_level=0:

optimization_level=2:

# run the circuits

sampler = Sampler(backend)

job = sampler.run([circ0, circ2], shots=10000)

job_id = job.job_id()

print(f"Job ID: {job_id}")

Job ID: d13rnnemya70008ek1zg

# REPLACE WITH YOUR OWN JOB IDS

job = service.job(job_id)

# get results

result = job.result()

unoptimized_result = result[0].data.meas.get_counts()

optimized_result = result[1].data.meas.get_counts()

from qiskit.visualization import plot_histogram

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, unoptimized_result, optimized_result]],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"with optimization",

],

)

4.3 回路合成の重要性

次に、2種類の異なる合成方法で作成した5量子ビットGHZ状態()準備回路の実行結果を比較します。

# Original GHZ circuit (naive synthesis)

ghz_circ.draw("mpl")

# A better GHZ circuit (smarter synthesis), you learned in a previous lecture

ghz_circ2 = QuantumCircuit(5)

ghz_circ2.h(2)

ghz_circ2.cx(2, 1)

ghz_circ2.cx(2, 3)

ghz_circ2.cx(1, 0)

ghz_circ2.cx(3, 4)

ghz_circ2.measure_all()

ghz_circ2.draw("mpl")

circ_org = pm2.run(ghz_circ)

circ_new = pm2.run(ghz_circ2)

print("original synthesis:")

display(circ_org.draw("mpl", idle_wires=False, fold=-1))

print("new synthesis:")

display(circ_new.draw("mpl", idle_wires=False, fold=-1))

original synthesis:

new synthesis:

# run the circuits

sampler = Sampler(backend)

job = sampler.run([circ_org, circ_new], shots=10000)

job_id = job.job_id()

print(f"Job ID: {job_id}")

Job ID: d13rp283grvg008j12fg

# REPLACE WITH YOUR OWN JOB IDS

job = service.job(job_id)

# get results

result = job.result()

synthesis_org_result = result[0].data.meas.get_counts()

synthesis_new_result = result[1].data.meas.get_counts()

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, synthesis_org_result, synthesis_new_result]],

bar_labels=False,

legend=[

"ideal",

"synthesis_org",

"synthesis_new",

],

)

4.4 一般的な1量子ビットゲートの分解

from qiskit import QuantumCircuit, transpile

from qiskit.circuit import Parameter

from qiskit.circuit.library.standard_gates import UGate

phi, theta, lam = Parameter("φ"), Parameter("θ"), Parameter("λ")

qc = QuantumCircuit(1)

qc.append(UGate(theta, phi, lam), [0])

qc.draw(output="mpl")

transpile(qc, basis_gates=["rz", "sx"]).draw(output="mpl")

4.5 1量子ビットブロックの最適化

from qiskit import QuantumCircuit

qc = QuantumCircuit(1)

qc.x(0)

qc.y(0)

qc.z(0)

qc.rx(1.23, 0)

qc.ry(1.23, 0)

qc.rz(1.23, 0)

qc.h(0)

qc.s(0)

qc.t(0)

qc.sx(0)

qc.sdg(0)

qc.tdg(0)

qc.draw(output="mpl")

from qiskit.quantum_info import Operator

Operator(qc)

Operator([[ 0.45292511-0.57266982j, -0.66852684-0.14135058j],

[ 0.14135058+0.66852684j, -0.57266982+0.45292511j]],

input_dims=(2,), output_dims=(2,))

from qiskit import transpile

qc_opt = transpile(qc, basis_gates=["rz", "sx"])

qc_opt.draw(output="mpl")

Operator(qc_opt)

Operator([[ 0.45292511-0.57266982j, -0.66852684-0.14135058j],

[ 0.14135058+0.66852684j, -0.57266982+0.45292511j]],

input_dims=(2,), output_dims=(2,))

Operator(qc).equiv(Operator(qc_opt))

True

4.6 トフォリ分解

qc = QuantumCircuit(3)

qc.ccx(0, 1, 2)

qc.draw(output="mpl")

from qiskit import QuantumCircuit, transpile

qc = QuantumCircuit(3)

qc.ccx(0, 1, 2)

qc = transpile(qc, basis_gates=["rz", "sx", "cx"])

qc.draw(output="mpl")

4.7 CUゲートの分解

from qiskit.circuit.library.standard_gates import CUGate

phi, theta, lam, gamma = Parameter("φ"), Parameter("θ"), Parameter("λ"), Parameter("γ")

qc = QuantumCircuit(2)

# qc.cu(theta, phi, lam, gamma, 0, 1)

qc.append(CUGate(theta, phi, lam, gamma), [0, 1])

qc.draw(output="mpl")

from qiskit.circuit.library.standard_gates import CUGate

phi, theta, lam, gamma = Parameter("φ"), Parameter("θ"), Parameter("λ"), Parameter("γ")

qc = QuantumCircuit(2)

qc.append(CUGate(theta, phi, lam, gamma), [0, 1])

qc = transpile(qc, basis_gates=["rz", "sx", "cx"])

qc.draw(output="mpl")

4.8 CX、ECR、CZはローカルクリフォードまで等価

(アダマール)、( Z回転)、( Z回転)、(パウリX)はすべてクリフォードゲートであることに注意してください。

qc = QuantumCircuit(2)

qc.cx(0, 1)

qc.draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["x", "s", "h", "sdg", "ecr"]).draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["h", "cz"]).draw(output="mpl", style="bw")

IBM バックエンドの1量子ビット基底ゲート "rz"、"sx"、"x" を使用します。

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["rz", "sx", "x", "ecr"]).draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["rz", "sx", "x", "cz"]).draw(output="mpl", style="bw")

# Check Qiskit version

import qiskit

qiskit.__version__

'2.0.2'