量子回路の実行

Olivia Lanes による量子回路とプリミティブに関する動画をご覧ください。または、YouTube で別ウィンドウで開くこともできます。

レッスンの概要

このレッスンでは、ユーティリティスケールの量子計算を実行するための基本事項を概観します。使用する量子ハードウェアから、量子回路を設計する際に考慮すべき原則までを扱います。このレッスンを終えるころには、以下のことを理解していただけるでしょう:

-

IBM® の量子コンピューターが実際にどのようなものか。量子回路を最適に設計してハードウェア上で実行するには、ハードウェアの基本的な特徴を知っておく必要があります。

-

Qiskit とは何か、プリミティブとは何か、そしてそれらを使って量子回路を作成・実行する方法。

-

大規模な実験を実行するための標準的なワークフロー。これには、ユースケースに最適なプリミティブの選択、問題を量子回路にマッピングすること、そしてエラー軽減・抑制の適用が含まれます。これらにより、ハードウェアの性能を最大限に引き出すことができます。

ハードウェア – IBM 量子プロセッサー

大規模な量子回路を設計する際に最適な選択をするためには、実際にその回路を実行するハードウェアについて少し知っておく必要があります。物理量子ビットと IBM 量子プロセッサーについて簡単に説明しましょう。

IBM の量子プロセッサーは、超伝導トランズモン量子ビットを使用して構築されています。これは ジョセフソン接合 とコンデンサーを並列に接続した電気回路です。ジョセフソン接合は、2 層の超伝導金属が絶縁バリアを挟んで重なり合うことで形成される非線形インダクターです。非常に低温になると、超伝導体内の電子が対を形成し、「クーパー対」と呼ばれる状態になります。クーパー対は、接合の絶縁バリアを自発的にトンネルして一方の側から他方へ移動することができます。このトンネル現象が非線形特性をもたらし、量子ビットが生成されます。

マイクロ波伝送線路がチップ上に作製され、量子ビットにマイクロ波信号を届けます。特定の周波数・振幅・形状・持続時間を持つ精密にキャリブレーションされたマイクロ波パルスを伝送線路に印加することで、量子ビットに特定の動作をさせることができます。これが量子ゲートの基礎となっています。チップは、隣接する量子ビットがヘビーヘックス格子と呼ばれる特定の格子構造で接続されるように製造されています。この接続性(いわゆるトポロジー)は、後述するように、回路を設計する際に考慮すべき重要な要素です。

マイクロ波パルスの命令は、あなたのコンピューターからクラウドを経由して室温制御エレクトロニクスに届き、そこで命令が解釈されてパルスが物理的に生成されます。室温制御ボックスがパルスを生成した後、�それはケーブルを通じて希釈冷凍機に入り、最終的に量子チップへと到達します。信号は共振器に入り、ワイヤーボンドを通過し、伝送線路を伝わって量子ビットへと流れ込みます。

IBM は世界中に数十台の量子コンピューターを保有しており、最近では 100 量子ビットを超えるプロセッサーのみで構成されるようにシステムを更新しました。その一部はニューヨーク州北部にある IBM 量子データセンターに設置され、クラウド経由で一般に公開されています。また、一部は IBM Quantum® Network のパートナー向けに専用のオンプレミスシステムとして提供されています。quantum.cloud.ibm.com にログインすると、アクセス可能なプロセッサーを確認できます。

各プロセッサーには 3 つのパフォーマンス指標が記載されています。前のレッスンで説明しましたが、改めて確認すると、量子ビット数・EPLG・CLOPS です。

-

量子ビット数(Qubit count)。 これは説明不要です。単一の量子プロセッサーで使用できる量子ビットの総数です。比較的大規模なユーティリティスケールの問題に取り組むには、問題に対応できるだけの十分な量子ビットを持つプロセッサーを使用する必要があります。ただし、量子ビット数だけが重要なわけではありません。

-

EPLG(layered gate あたりのエラー数)。 これは量子ビットと量子ゲートの品質の尺度です。100 量子ビットの連鎖で隣接量子ビットをエンタングルする回路において、各ゲートが導入する平均エラー率を測定します。この値はできるだけ小さいほ��ど望ましいです。

-

CLOPS(1 秒あたりの回路層演算数)。 これはプロセッサーの速度を定量化します。量子プロセッシングユニット(QPU)が単位時間あたりに実行できる量子ボリューム回路と呼ばれるベンチマーク回路の層数を測定します。数値が高いほど、計算が速くなります。

これらの指標の重要度は、具体的なアプリケーションによって異なります。今後のレッスンでは、これらの要素が計算結果にどのような影響を与えるかを実際の例で確認していきます。

ソフトウェア:Qiskit と Qiskit Runtime

量子問題を量子コンピューターへの命令に変換するには、IBM が開発した量子コンピューター向けのオープンソースソフトウェア開発キットである Qiskit を使用します。また、Qiskit のコア機能を基盤として構築・拡張するソフトウェアチュートリアルや関数のコレクションである Qiskit エコシステムと、Qiskit Runtime プリミティブを使用して量子ワークロードを設計・最適化し、効率的に実行できる量子コンピューティングサービス・プログラミングモデルである Qiskit Runtime もあります。

プリミティブは、より大きな回路やジョブを設計するために使用できる小さなビルディングブロックです。最も重要な 2 つのプリミティブは、サンプラーとエスティメーターであり、まもなく詳しく説明します。

最近リリースされた Qiskit v1.0 により、Qiskit はこれまで以上に高性能で安定したものになりました。これから始める方にとっては、絶好のタイミングです!すでに Qiskit に慣れ親しんでいる方は、最新バージョンをダウンロードして再インストールする必要があります。完全なインストールガイドは、Qiskit のインストールガイドをご覧ください。

量子回路

いよいよ量子プログラムの基盤となる量子回路について説明します。このセクションは復習としての位置づけです。量子回路に慣れていない方は、続きを読む前に「量子情報の基礎」コースの量子回路レッスンで詳しく学ぶことをお勧めします。

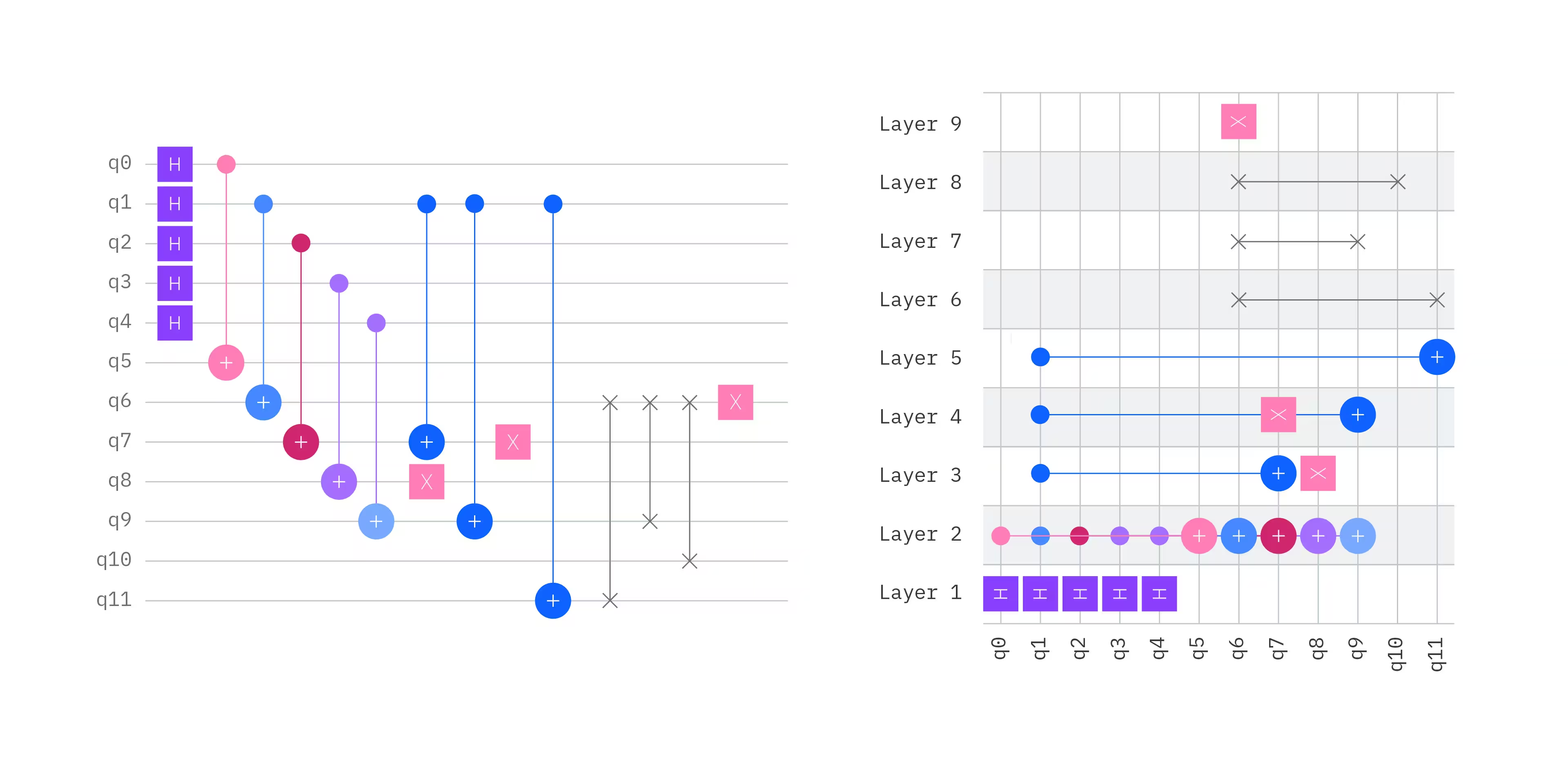

量子回路は、量子ビットを表す導線によってつながれた量子ゲートと測定のネットワークであり、以下に示すようなものです。量子回路は楽譜のように左から右へ読み、左端の時刻 0 から始まります。物理的な量子ビットにまだ割り当てられていない仮想量子ビットは、上から下に向かって昇順にリストされます。

ゲートは、関係する量子ビットの導線上に異なるシンボルで表されます。単一量子ビットゲート(下図のアダマールゲート、H と書かれたボックス)は、その導線上の量子ビットにのみ影響します。マルチ量子ビットゲート(下図の CNOT ゲート、q0 に線がつながった円の中のプラス記号)は 2 つ以上の量子ビットに影響�します。示されている CNOT ゲートでは、q1 の状態が q0 の状態に応じて変化します。すべてのゲートが実行された後、量子ビットを測定することができます。測定は黒いゲートに測定記号で示されています。測定結果は古典レジスター(下の二重線の「meas」バス)に書き込まれます。

回路の重要な特性の一つが深さです。量子回路の深さとは、回路を完成させるために並列実行される量子ゲートの「層」の最小数です。共通の量子ビットを持たないゲートは並列(同時)に実行できます。しかし、同じ量子ビットに 2 つ以上のゲートが作用する場合、それらは並列に実行できず、別々の層で順番に実行する必要があります。

回路の深さを求めるもう一つの、あまり明白ではない方法があります。これはある種のゲームで行います。ルールは単純です。左側の任意の量子ビット導線から始め、右に進みながらパスで遭遇したゲートの数を数えます。マルチ量子ビットゲートで現在の導線に接続されているときのみ、隣の導線にジャンプできます。目標は、パスで遭遇するゲートの数を最大化することです。この最大数が回路の深さと一致します。

量子ゲートの実装には時間がかかるため、回路の深さは量子コンピューターが回路を実行するのに必要な時間にほぼ対応します。プロセッサー上の量子ビットのデコヒーレンス時間によって、大きな深さの回路に適したマシンとそうでないマシンがあります。そのため、特定のデバイスで回路を実行できるかどうかを判断するには、回路の深さを知る必要があります。

量子回路の設計:Qiskit パターン

では、量子回路を設計・実行するにはどのように進めればよいでしょうか?典型的な量子コンピューティングワークフローを理解する最も簡単な方法は、Qiskit パターンを通じてです。Qiskit パターンは、モジュール式ツールを使って特定のステップを実装することで量子ワークロードを実行できる概念的なフレームワークです。これにより、量子コンピューティングのタスクを強力なヘテロジニアス(CPU/GPU/QPU)コンピューティングインフラで実行できます。各ステップはサービスとして提供可能で、リソース管理を組み込むことができ、新しい機能が開発されるにつれてシームレスな組み合わせが可能です。

主なステップは以下のとおりです。経験豊富な Qiskit ユーザーには見覚えがあるでしょう。

-

マップ(Map)。 このステップでは、取り組みたい一般的な問題を量子回路という形式で量子コンピューターにどのようにマッピングするかを形式化します。

-

最適化(Optimize)。 このステップでは、Qiskit のトランスパイラーを使用して、実際の物理量子ビットハードウェアに回路を配置・ルーティングします。これには、個々の量子ゲートをハードウェア上で実行される演算のシーケンスに変換することや、ゲートの配置の最適化が含まれます。

-

実行(Execute)。 Qiskit Runtime プリミティブは、トランスパイルされた回路を実行できる IBM Quantum ハードウェアへのインターフェースを提供します。このステップには、ユー�ザーから抽象化されたエラー抑制・軽減技術の適用も含まれます。

-

後処理(Post-process)。 このステップでは、量子プロセッサー自体から得られたデータを処理し、元の問題に対する有用な結果をユーザーに提供します。基本的に、取得したデータのさらなる分析を包括します。

マップ

マップステップは本質的に「この問題を量子ハードウェアで合理的に実行できる量子回路にどのように変換するか?」という問いに答えるものです。マッピングは難しい問題であり、現在も活発に研究されている分野です。成功を保証する確実な方法はありませんが、推奨されるガイドラインと、すでにマッピング方法が分かっている問題の例があります。

最初のガイドラインは、古典コンピューターが得意なことは古典コンピューターにやらせることです。古典コンピューターで簡単にできるタスクは、量子コンピューターの恩恵を受けられないでしょう。量子コンピューターは古典的に難しい問題のためのものです。もちろん、Qiskit や量子コンピューターを初めて使う場合は、計算量的に複雑な問題を見つけることに固執する必要はありません。ユーティリティスケールのプロジェクトに直接取り組む前に、学習のために解決できる小さく扱いやすい問題に分解しましょう。

次に、測定または理解したい問題の結果を期待値またはコスト関数に変換します。コスト関数は、問題の目標を最小化または最大化すべきものと��して定義する問題固有の関数です。試行状態または解が目標に対してどれだけうまく機能しているかを評価するために使用できます。この概念は、化学・機械学習・金融・最適化などのさまざまなアプリケーションに適用できます。どの分野から問題にアプローチしているかは必ずしも関係ありません。

また、使用するハードウェアには特定のトポロジーがあることも念頭に置いてください(ハードウェアのセクションで説明したとおり)。接続されている量子ビットと接続されていない量子ビットがあります。IBM 量子プロセッサーのヘビーヘックストポロジーに準拠した回路に問題をマッピングする必要があります。

今のところ最も重要なことは、このステージには練習が必要だということです。問題だけでなく、ハードウェアの能力についても十分な理解が必要です。将来のレッスンでは、これらすべての考慮事項をバランスよく扱う方法を具体的な例とユースケースを通じて確認していきます。

最適化

次に、回路を実行するのに十分な数の高品質な量子ビットを持つ量子プロセッサーを選択する必要があります。ハードウェアセクションで説明した 3 つの指標(量子ビット数・EPLG・CLOPS)を参考にしてこの決定を行いましょう。

次に、選択したハードウェア向けに回路を最適化します。まず、回路を効率的に配置・ルーティングする必要があります。レイアウトとは、回路内の仮想量子ビットをプロセッサー上の物理量子ビットにマッピングすることです。ルーティングとは、回路内の仮想量子ビット間の接続性がプロセッサー上の物理量子ビットの接続性に一致するように回路を調整することです。レイアウトとルーティングの段階で念頭に置くべきことがいくつかあります。

-

すべての量子ビットが接続されているわけではありません。チップ上でお互いに非常に遠い位置にある量子ビットも存在し、できる限り長距離の相互作用を減らすか排除する必要があります。隣接する量子ビット間に SWAP ゲートのシーケンスを適用して量子ビットの情報を移動させることはできますが、SWAP ゲートはコストが高くエラーが発生しやすいため、より良い方法があるかもしれません。コストの高い SWAP ゲートは避けるようにしましょう。

-

レイアウトとルーティングは反復的なプロセスです。手動で行うこともできますが、近似エラー率に基づいて物理量子ビットのレイアウトを推薦する

mapomaticという Qiskit ツールもあります。トランスパイラー(まもなく説明します)も情報に基づいた提案ができます。

次に、同じ量子ビットに作用する 1 量子ビットゲートのシーケンスを単一のゲートに合成できます。また、不要なゲートやゲートの組み合わせを排除できる場合もあります。たとえば、ゲートの組み合わせによっては、より単純な組み合わせに簡略化できる場合があります。実際、ゲートの組み合わせが恒等演算と等価になることもあり、その場合は単純に排除できます。これは Qiskit トランスパイラーを使って自動的に行えますが、より細かく制御したい場合はゲートごとに手動で行う��こともできます。

回路のレイアウト・ルーティング・ゲート数を(手動またはトランスパイラーを使って)改善したら、通常は回路を視覚化して、すべてのゲートのタイミングが理にかなっているか確認します。トランスパイラーにはフラグを指定して回路のタイムラインを視覚化し、すべてが期待どおりに配置されていることを確認できます。

Qiskit トランスパイラー

前述のとおり、Qiskit トランスパイラーはパターンワークフローの初期段階で役立ちます。では、その機能をより詳しく見ていきましょう。トランスパイラーは、特定の量子デバイスのトポロジーに一致するように入力回路を書き換え、実行とノイズへの耐性を最適化できます。また、選択した特定の量子プロセッサーの基底ゲートに回路を書き換えます。

Qiskit には、異なる最適化レベルに対応する 4 つの組み込みトランスパイルパイプラインがあります。量子回路の最適化にすでに精通していない限り、そのいずれかを使用することをお勧めします。デフォルトでは、トランスパイルプロセスには以下の 6 つのステップが含まれます:

-

初期化(Initialization)。このステージでは、バックエンドへの回路の埋め込みを開始する前に必要な初期パスを実行します。通常、カスタム命令を展開し、回路を単一および 2 量子ビットゲートのみに変換します。

-

レイアウト(Layout)。このステージでは�、回路内の仮想量子ビットをバックエンドの物理量子ビットにマッピングします。詳細はレイアウトステージをご参照ください。

-

ルーティング(Routing)。このステージはレイアウトが適用された後に実行され、元の回路にゲート(SWAP ゲートなど)を挿入して、バックエンドの接続性と互換性を持たせます。詳細はルーティングステージをご参照ください。

-

変換(Translation)。このステージでは、回路内のゲートをターゲットバックエンドの基底セットに変換します。詳細は変換ステージをご参照ください。

-

最適化(Optimization)。このステージでは、特定の条件(ターゲットの深さへの到達など)が満たされるまで、メインの最適化ループを繰り返し実行します。以下で説明する 4 つの異なる最適化レベルから選択できます。

-

スケジューリング(Scheduling)。このステージは、ハードウェアを考慮したスケジューリングパスのためのものです。大まかに言えば、スケジューリングは、命令実行間の量子ビットのアイドル時間を考慮して回路に遅延を挿入することと考えることができます。

最適化レベルは 0 から 3 の 4 段階で、高い最適化レベルほど時間と計算リソースがかかりますが、より優れた回路が得られる可能性があります��。最適化レベル 0 はデバイス特性評価実験を目的としており、最適化を実行せずに入力回路をターゲットバックエンドの制約にマッピングするだけです。最適化レベル 3 は最も多くの労力を費やして回路を最適化します。ただし、トランスパイラーの最適化技術の多くはヒューリスティックに基づいているため、より多くの計算リソースを使っても出力回路の品質が向上するとは限りません。さらに詳しく知りたい方は、Qiskit ドキュメントのトランスパイラードキュメントをご覧ください。

エラー抑制

回路のエラーを削減する最初のステップは、(トランスパイラーを使うか手動で)すでに行ったレイアウト・ルーティングの最適化とゲート数の最小化です。次に、より高度なエラー抑制の方法について説明しましょう。

エラー抑制とは、コンパイル中に回路を変換してエラーを最小化する技術のクラスを指します。これは後述する「実行」セクションで扱うエラー軽減とは異なります。使用する最も一般的な 2 つのエラー抑制の形態は、動的デカップリングと Pauli ツワーリングです:

- 動的デカップリングは、量子ビットがアイドル状態にある間に導入される環境ノイズの一部を効果的にキャンセルするために使用されます。特定のタイミングで一連のゲートを適用することで、アイドル期間の一方で蓄積されるノイズが��他方のノイズを近似的にキャンセルするようにできます。

- Pauli ツワーリングは、動的デカップリングのようにノイズをキャンセルするためではなく、ノイズを単純化するためにランダムなゲートを挿入する方法です。ランダムなゲートを挿入することで、さまざまなエラーの影響が蓄積されるスピードを抑え、ノイズが確率的な性質を持つようになるため、後処理での修正や除去が容易になります。この手法はまた、以下で説明する強力なエラー軽減技術の基礎にもなっています。

実行

これで量子プログラムを実行する準備ができました。Qiskit Runtime プリミティブは IBM Quantum ハードウェアへのインターフェースを提供し、エラー抑制・軽減をユーザーから抽象化します。選択できるプリミティブは 2 つあります:サンプラーとエスティメーターです。

Qiskit Runtime のサンプラーは、量子デバイス上で回路を複数回実行し、各実行で測定を行い、取得したビット文字列から確率分布を再構築します。実行回数(ショット数)が多いほど結果の精度は高くなりますが、より多くの時間と量子リソースが必要になります。具体的には、回路によって準備された状態を測定することで、各標準基底状態を得る確率を計算します。

Qiskit Runtime のエスティメーターは、複雑な代数的プロセスを使用して、オブザーバブルを既知の固有基底を持つ他のオブザーバブルの組み合わせに分解することで、実際の量子デバイス上での期待値を推定します。

実行ステップでは、エラー軽減戦略も選択できます。エラー軽減とは、実行時に存在したデバイスのノイズをモデル化することで、回路エラーを削減できる技術を指します。通常、これによりモデルトレーニングに関連する量子前処理オーバーヘッドと、生成されたモデルを使用して生の結果のエラーを軽減する古典後処理オーバーヘッドが生じます。このオーバーヘッドと引き換えに、はるかに精度の高い結果を得ることができます。

エラー軽減には複数の技術を実装できます。ここでは、エラーへの耐性が増す順(ただし計算コストも増す順)に 3 つを説明します。ただし、これは現在も活発に研究されている分野であることに注意してください。新しい技術が開発され、既存の技術が改善され続けるでしょう。

レジリエンスレベル 0 では、トランスパイラーは回路に対して何も行いません。

レベル 1 では、Twirled Readout Error eXtinction(T-REX)と呼ばれる方法が導入されます。T-REX は、エラー抑制セクションで説明した Pauli ツワーリングを使用します。前述のように、ランダムなゲートを回路に挿入することで、非常に複雑でモデル化が難しいノイズでも確率的に見せることができ、後処理での修正や除去がはるかに容易になります。

レジリエンスレベル 2 では、Zero Noise Extrapolation(ZNE)が追加されます。これは最近多くの成功を収めている人気の技術です。ZNE の背景にある考え方は少し驚くかもしれません。実際に、すでに存在するノイズの上にさらにノイズを追加するのです!しかし、これにより逆方向に外挿することができ、ノイズがどんどん少なくなった場合の結果がどのようになるかを予測できます。

ノイズを追加するにはいくつかの方法があります。たとえば、ゲートを引き伸ばして長くすることでエラーが起きやすくしたり、最終的に恒等演算になる追加のゲートを実行して、回路の機能は変えずに意図的により多くのノイズをサンプリングしたりする方法があります。ただし、追跡したいすべての回路とすべての期待値についてこれを行う必要があります。そのため、計算コストが高くなる可能性があることがわかります。

ZNE の特定のタイプに Probabilistic Error Amplification(PEA)と呼ばれるものがあります。ゲートのノイズモデルを学習した後、PEA はそのノイズモデルからエラーをサンプリングし、意図的に回路に注入することで機能します。これはまだ Qiskit では利用できませんが、今年後半に利用可能になる予定です。

最後に説明するエラー軽減の形態は Probabilistic Error Cancellation(PEC)です。PEC は第 3 レジリエンスレベルにあるのではなく、Qiskit で手動で有効にする必要がある特別な機能です。これは、必要な計算リソースが他のエラー軽減技術に比べてスケールしにくいためです。まず、回路に影響を与えているノイズについて学習するところから始めます。回路内の 2 量子ビットゲートの各固有層に対してノイズ学習または特性評価回路を実行します。これらの結果により、ノイズを Pauli 演算子の形で記述できるようになります。これらのノイズ項が分かれば、ノイズチャネルをキャンセルする反対の Pauli ゲートを効果的に組み込むように回路を変更できます。このプロセスはある意味、ノイズキャンセリングヘッドフォンの仕組みに似ています。しかし、このノイズを打ち消す方法はコストが非常に高く、ゲート数に対して指数関数的に実行時間が増加するため、非常に大きな回路には最適な選択肢ではないかもしれません。

後処理

後処理ステージは、量子回路の出力を視覚化・分析する段階です。これには、視覚化モジュールや量子情報モジュールなど、多数の Qiskit ツールが利用できます。ここでは詳しく説明しませんが、今後のレッスンでアプリケーションの例に踏み込む中で、これらのモジュールが実際に動作する様子を見ていきます。

まとめ

このレッスンでは、ユーティリティスケールの量子計算を実行する際の主な考慮事項とワークフローを駆け足で紹介しました。情報が盛りだくさんで、実際の例で理論的な概念が実践されるのを見るまでは、なかなか理解が定着しないかもしれません。だからこそ、このコースの残りはそういった実例で構成されています。このコースが「実践的な量子コンピューティング(Quantum Computing in Practice)」と呼ばれているのも、伊達ではありません!

次回は、Qiskit パターンワークフロー�を使用して、グラフ理論の古典的な問題である MaxCut を解く量子回路を設計・実行する具体的な例を見ていきます。